Depuis 2019, le projet SPOC s’est construit autour d’une collaboration entre Airbus Defence & Space, Viveris Technologies et l’IRT Saint Exupéry pour rendre industrialisable des techniques et méthodes d’intelligence artificielle sur des plateformes SoC (System On a Chip) à base de CPU (Central Processing Unit), GPGPU (General-purpose Processing on Graphic Processing Units) ou FPGA (Field Program Based Arrays).

L’OBJECTIF DU PRODUIT

The SPOC (Software Payload On Chip) project teams study ways to integrate Machine Learning on embedded systems for the space, droning and industrial domains.

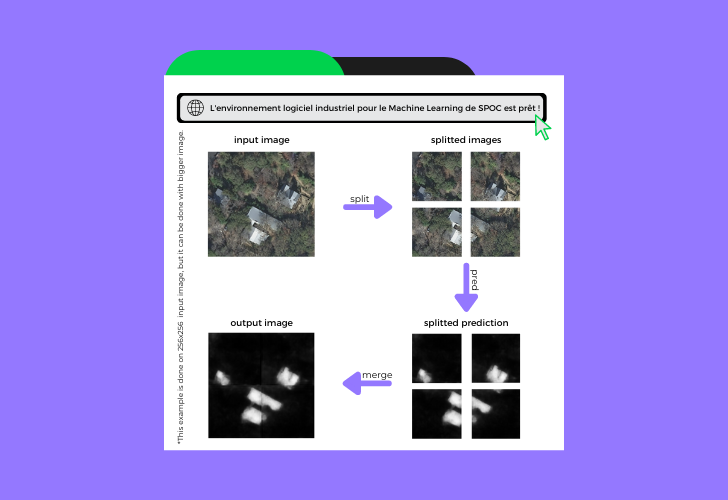

L’objectif du projet est de pouvoir implémenter un réseau neuronal de moyenne/grande taille à bord d’une plateforme d’acquisition d’images embarquée pour diminuer le taux de transfert de données brutes vers le sol.

A ce jour, des solutions sont déjà existantes mais ne sont pas réellement utilisable car trop gourmandes en termes de consommation d’énergie, de puissance de calcul, de volumétrie et même de temps de mise en œuvre.

L’étude menée par le projet SPOC a permis de rechercher le meilleur compromis entre ces contraintes en réalisant différentes mesures (performance, puissance, qualité, pertinence, …) sur deux niveaux de cible que sont les GPGPU (avec une carte JETSON) et les FPGA (avec une carte XILINX Ultrascale).

L’ENVIRONNEMENT DU DEVELOPPEMENT

Pour permettre une mise en route et un déploiement rapide sur de futurs projets industriels, l’équipe SPOC a mis en place un flow automatisé de construction de projet au travers des outils Docker et GitLab-CI.

A l’aide de cet environnement, les développeurs se concentrent uniquement sur la phase de conception, de développement du logiciel et de correction de défauts sur cible. Ils sont déchargés des tâches de génération de exécutables (binaires et bitsream) qui sont automatiquement produites par le système.

LE DEVELOPPEMENT

La prochaine étape majeure sera de mesurer et valider les différentes métriques sur l’ensemble des cibles choisies et d’optimiser / qualifier les modèles utilisés pour terminer le projet à la fin du premier semestre 2022.

This study focuses on the evaluation of both GPGPU and FPGA technologies to enable maximum parallelization on the neural network. The

Cette étude porte à la fois sur l’évaluation des technologies GPGPU et FPGA pour permettre une parallélisation maximale sur le réseau neuronal.

Les développements associés au GPGPU ont été réalisés dans un premier temps sur un PC standard avec une carte graphique NVIDIA GX3070 où nous avons déployé la solution avec le Framework Tensorflow / Keras codé en Python ; toute la phase de choix de modèle et d’entrainement a été réalisée avec cette même solution. Nous avons par la suite porté cette solution sur la carte JETSON AGX XAVIER avec succès.

L’étape suivante sera de réaliser l’ensemble du développement en langage C/C++ avec le Framework cuDNN en version 8.0.x ou supérieure. Le but de cette prochaine phase sera de valider une optimisation et d’obtenir un gain de performance non-négligeable sur l’exécution des modèles choisis.

En parallèle, les développements associés au FPGA ont été réalisés sur une cible ZYNQ UltraScale+ ZCU102 et l’outil Vivado 2020.1. Les FPGAs permettent de tester différentes méthodes d’inférence. A ce jour différentes solutions ont été étudiées, telle que le DPU (DeepLearning Processor Unit) de Xilinx, le VTA (Versatile Tensor Accelerator) et les accélérateurs personnalisés avec HLS4ML.

Avec l’apparition d’accélérateurs matériels dans les data centers et les périphériques « On the edge », la spécialisation matérielle a joué un rôle de premier plan dans les systèmes de DeepLearning.

La technologies DPU (DeepLearning Processor Unit) est un accélérateur programmable dédié aux réseaux de neurones convolutifs. VTA (Versatile Tensor Accelerator) a l’avantage, contrairement au DPU, d’être open source.

Les caractéristiques matérielles des solutions

Ordinateur fixe avec RTX-3070 :

Pour un prototypage rapide réalisée en Python avec des Frameworks classiques sans se soucier des contraintes d’encombrement, de prix et de consommation.

o CPU : i7-11700 8-core 2.9GHz 64-bit CPU

o GPU : 5888-core Ampere GPU with RT & Tensor Cores

o MEM : 4x16Go DDR4 3200 PC25600

o Storage : Kingston 1To SSD M.2 NVMe

JETSON AGX XAVIER:

Pour des projets industriels moderne et valider une architecture GPU beaucoup moins consommatrice en énergie et avec un faible encombrement.

o CPU : 8-core ARM v8.2 64-bit CPU, 8MB L2 + 4MB L3

o GPU : 512-core Volta GPU with Tensor Cores

o MEM : 16GB 256-Bit LPDDR4x | 137GB/s

o Storage : 32GB eMMC 5.1

ZYNQ UltraScale+:

Pour des projets industriels avec contrainte spécifique et valider une architecture DPU moins gourmande en énergie et une modularité plus adaptée.

o CPU : quad-core Arm® Cortex®-A53 64-bit CPU

o Logic Cells : 600k

o MEM : PS-4GB DDR4 / PL-512MB DDR4

o Storage : Dual 64MB Quad SPI flash

A l’heure actuelle du projet, tous les environnements sont opérationnels, les apprentissages sur les modèles sélectionnés sont réalisés et les développements des accélérateurs pour le FPGA ainsi que les opérations unitaires du GPGPU sont en cours de développement et d’optimisation.

Toute l’équipe SPOC remercie ses partenaires industriels : Viveris Technologies, Airbus Defence & Space et l’IRT Saint Exupéry.